1. SDR和DDR

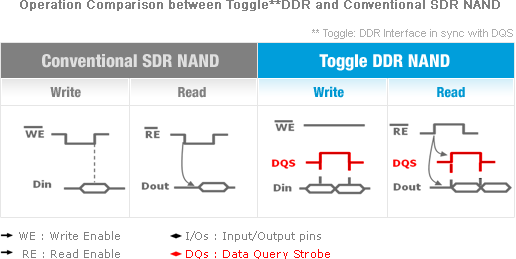

- SDR(Single Data Rate),写读数据使用上升沿或下降沿来触发。因为只用上升沿或下降沿,对信号准确性要求较低。

- DDR(Double Data Rate),写数据时通过MCU来控制DQS信号跳变沿来触发(即上升沿和下降沿均触发),所以对信号的准确性要求较高,(同步)可以通过增加同步时钟信号来提高信号的准确性,如ONFI2.0时的DDR就是使用此方式。(异步)另外还可以通过差分信号来提高信号准确性,Toggle下的DDR,ONFI3.0/ONFI4.0下的DDR也都支持DQS差分信号(DQS_t,DQS_c)来进行DDR操作。2. Sync和Async

2. Sync和Async

- Sync模式是指Flash操作时需要一个源时钟来对锁存信号进行同步,提高信号采集的准确性。因为另外一个源时钟信号来进行同步,所以对Flash的品质要求较高,如果信号不稳定,很容易导致源时钟信号与锁存信息不对应,导致数据采样不准确。Sync模式的Flash一般支持Async,当品质不达标时,便采用Async模式操作。

- Async,即不需要时钟信号来进行同步,数据通过WEN/REN来锁存。在未使用DDR的时候,Async方式的操作效率是比Sync效率低。因为Sync模式有时钟同步,信号较准确,所以可以提高采样率。Async模式为了提高效率,所以必须采用某种方式提升信号准确性。这 个时候,采用了差分信号,大幅提升了信号的准确性,为此采用了DDR模式采样数据。

3. ONFI和Toggle

-

- ONFI(Open Nand Flash Interface),由Hynix、Inter、Micron、Phison、Sony、Spansion于2006年共同创建的一个Nand Flash的接口标准,并于当年发布了ONFI1.0标准,支持SDR。ONFI2.0时增加NV-DDR,支持DDR操作,不过是使用同步时钟来控制的。ONFI3.0时,增加NV-DDR2,ONFI4.0时增加了NV-DDR3。NV-DDR2和NV-DDR3都是支持DQS差分信号而不用同步时钟的。并且ONFI接口都是同步向前兼容的。但是接口间的转换只支持如下几种:(详见ONFI Spec)

• SDR to NV-DDR

• SDR to NV-DDR2

• NV-DDR to SDR

• NV-DDR2 to SDR - Toggle,是Samsung和Toshiba以DDR为基础制定的Flash接口标准,是为了对抗ONFI的标准。Toggle1.0对应DDR1,Toggle2.0对应DDR2。Toggle接口的Flash一般也支持切换到Legacy接口(即SDR,和ONFI1.0是相同的)。Toggle接口Flash一般启动时是Legacy Mode,需要设置才能进入Toggle Mode(DDR1/DDR2),同样在Toggle模式下也可以设置命令序列进入Legacy Mode(SDR)。

- 除了ONFI2.0时的NV-DDR1是需要同步时钟外,其他接口下都是Async模式。所以我们常说从DDR模式切换到Async模式是不太准确的说法。应该说切换到Legacy Async、Traditinal Async或是SDR模式。

- ONFI(Open Nand Flash Interface),由Hynix、Inter、Micron、Phison、Sony、Spansion于2006年共同创建的一个Nand Flash的接口标准,并于当年发布了ONFI1.0标准,支持SDR。ONFI2.0时增加NV-DDR,支持DDR操作,不过是使用同步时钟来控制的。ONFI3.0时,增加NV-DDR2,ONFI4.0时增加了NV-DDR3。NV-DDR2和NV-DDR3都是支持DQS差分信号而不用同步时钟的。并且ONFI接口都是同步向前兼容的。但是接口间的转换只支持如下几种:(详见ONFI Spec)

ONFI接口标准

ONFI(Open NAND Flash Interface)标准是由英特尔,镁光,海力士,台湾群联电子,SanDisk, 索尼,飞索半导体为首宣布统一制定的连接NAND闪存和控制芯片的接口标准,当初制定ONFI标准的主要目的是统一当时混乱的闪存标准。

2006年,随着手机、MP3播放器、U盘的需求量逐渐增大,以及开始步入消费市场的SSD,市场对NAND闪存的需求也增加不少,而当时各个闪存制造厂所用的设计标准各有不同,这样导致闪存控制器厂商和下游产品制造厂在制作产品时碰到各种麻烦,业界迫切需求一个统一的标准,这就是ONFI的诞生背景。

ONFI 1.0制定于2006年12月,内容主要是制定闪存的物理接口、封装、工作机制、控制指令、寄存器等规范,增加对ECC的支持,传输带宽从传统的Legacy接口的40MB/s提升到50MB/s,性能提升幅度不大,不过其主要目的还是统一闪存接口规范,减轻产品厂商的开发压力。

ONFI 2.0标准诞生于2008年2月,2.0标准将带宽速度提高到133MB/s以满足高速设备对闪存性能的需求,在该版本中,主要是通过两项技术来提高传输速度。第一项就是在DRAM领域里常用的DDR(Double Data Rate,双倍数据率)信号技术。第二项是使用源同步时钟来精确控制锁存信号,使其能够达到更高的工作频率。

ONFI 2.1标准于2009年1月发布,带宽提升到166MB/s和200MB/s(工作模式不同速度不同),8KB page数据传输延时降低,改良电源管理降低写入操作能耗,加强ECC纠错能力,新增“Small Data Move”与“Change Row Address”指令。

ONFI 2.2发表于2009年10月,增加了LUN(逻辑单元号)重置、增强页编程寄存器的清除和新的ICC测量和规范。LUN重置和页编程寄存器清除提升了拥有多个NAND闪存芯片设备的处理效率,ICC规范则简化了下游厂家的测试程序。

ONFI 2.3在2010年8月的闪存峰会上发布,在2.2标准的基础上加入了EZ-NAND协议。EZ-NAND是Error Zero NAND的简写,这一协议将NAND闪存的纠错码管理由主控芯片中转移到闪存自身,以减轻主控芯片负担。

ONFI 3.0规范发布,接口带宽提升到400MB/s,需求的针脚数更少让PCB走线更加方便,从目前披露的资料来看,ONFI 3.0采用更短的信道、更宽的信号间距,并加入片内终止技术,使其传输带宽能够达到400MB/s。

三星与东芝的ToggleDDR阵营

面对ONFI组织的攻势,占有全球70% NAND产能的两大闪存生产巨头三星与东芝决定携手对抗,2007年12月,三星与东芝联合通过了一项关于闪存专利技术互换授权协议,根据这项协议,三星电子和东芝在闪存规格和技术上将完全共享。

根据项协议规定,三星将允许东芝生产和制造自己旗下的OneNAND和Flex-OneNAND闪存芯片,而东芝公司则将以自己的LBA-NAND和mobileLBA-NAND闪存芯片技术作为条件与三星电子进行交换,这些闪存芯片生产技术都是三星电子和东芝的核心技术,但是新的合作协议让双方在闪存芯片制造技术实力上都取得了进一步的增强,此外他们将一同合作研发新一代闪存产品,也就是后来的Toggle DDR NAND闪存。

2010年6月三星与东芝开始投产符合Toggle DDR 1.0接口标准的NAND闪存,Toggle DDR NAND采用双向DQS信号控制读写操作,信号的上升与下降沿都可以进行资料的传输,能使传输速度翻倍,接口带宽为133MB/s,而且没有内置同步时钟发生器(即NAND还是异步设计),因此其功耗会比同步NAND更低。

2010年8月,最新的Toggle DDR 2.0接口标准发布,传输带宽上升到400MB/s,关于此标准的详细消息还不多,不过可以可以确定的是技术指标与ONFI 3.0是类似的。

闪存的同步与异步

我们经常说闪存的同步与异步模式,其实是在ONFI 2.0标准中新加入的特性(ToggleDDR不存在同步闪存的情况,均为异步设计,但性能仍然强悍),ONFI 2.0标准在NAND中加入了同步时钟发生器,主控可以通过发送同步指令激活闪存上的同步时钟信号,使闪存工作在同步模式 ,此时闪存的数据传输速率会大幅度提升,异步模式相当于ONFI 1.0,闪存的带宽为50MB/s,而同步模式下闪存至少也符合ONFI 2.0,闪存带宽可达到133MB/s以上。

实际上同步与异步闪存都是同一生产线上下来的,颗粒品质的优劣才产生了这样的区别。比如英特尔29F64G08AAME1颗粒属于异步闪存,而英特尔29F32B08JCME2则支持同步/异步模式,又如镁光的29F64G08CBAAA是异步闪存,而29F64G08CBAAB颗粒支持同步/异步模式。

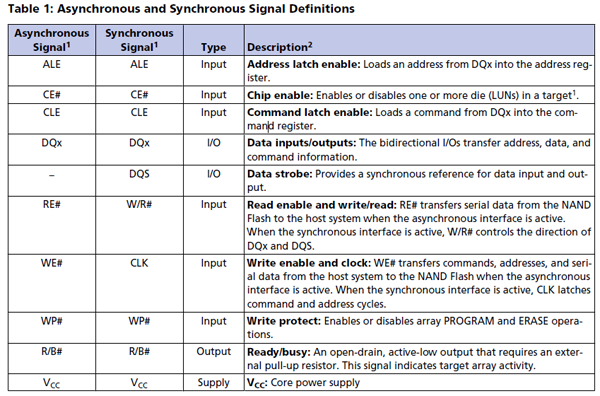

开机时SSD是运行在异步模式的,只有当主控发送同步指令给闪存后,才激活闪存上的源同步时钟,然后针脚定义发生改变,激活DQS信号, 让其工作在同步模式,并将异步模式下的WE#信号变为CLK信号,RE#变为W/R信号,同步模式下DQS信号的上升沿与下级沿都能控制信号的传输,使传输速度翻倍。

市面上有少数SSD使用异步闪存,但强制运行在同步模式,性能是上来了,稳定性存在隐患。